In the realm of Very Large Scale Integration (VLSI) design, congestion is a critical challenge that can significantly impact the performance and manufacturability of integrated circuits (ICs). This blog post delves into the causes of congestion in VLSI, its implications, and effective strategies for mitigation. Our aim is to provide a comprehensive guide that ranks high in Google search results, adhering to the best SEO practices outlined by Yoast SEO and ensuring excellent readability.

What is Congestion in VLSI?

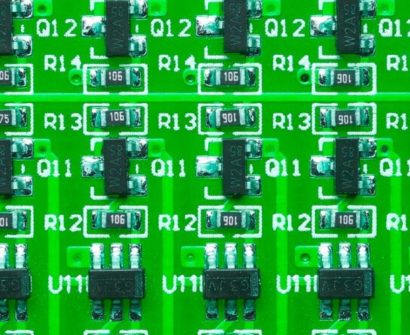

Congestion in VLSI refers to the overcrowding of routing paths within an integrated circuit. This occurs when the demand for routing resources exceeds the available capacity, leading to performance degradation, timing issues, and increased power consumption. Effective congestion management is crucial for ensuring the optimal functioning of VLSI designs.

Causes of Congestion in VLSI

- High Density of Components: As the density of transistors and other components increases, the available space for routing decreases, leading to congestion.

- Complex Routing Paths: Complex designs often require intricate routing paths, which can lead to congestion in specific areas of the chip.

- Suboptimal Floorplanning: Poor floorplanning can result in uneven distribution of components, causing localized congestion.

- Inadequate Routing Resources: Limited routing resources in certain areas of the chip can lead to bottlenecks.

- Increased Design Complexity: Advanced designs with multiple layers and high interconnectivity can exacerbate congestion issues.

Implications of Congestion in VLSI

- Performance Degradation: Congestion can cause delays in signal propagation, leading to timing violations and reduced performance.

- Higher Power Consumption: Congested areas may require additional buffers and repeaters, increasing power consumption.

- Manufacturing Challenges: Congested designs are harder to manufacture, potentially leading to lower yield and higher costs.

- Thermal Issues: Increased activity in congested areas can lead to hotspots, causing thermal management problems.

Strategies to Mitigate Congestion in VLSI

- Optimal Floorplanning: Effective floorplanning helps distribute components evenly across the chip, reducing congestion.

- Tip: Use automated tools for initial floorplanning and manual adjustments for fine-tuning.

- Efficient Placement and Routing: Use advanced placement and routing algorithms to minimize congestion.

- Tip: Tools like Cadence Innovus and Synopsys IC Compiler II can help optimize placement and routing.

- Layer Optimization: Utilize multiple metal layers effectively to distribute routing paths and reduce congestion.

- Tip: Consider adding more layers in congested areas if the manufacturing process allows.

- Buffer Insertion: Strategic buffer insertion can help alleviate congestion by reducing signal delays and balancing load.

- Tip: Automated buffer insertion tools can optimize the process.

- Routing Congestion Analysis: Perform regular congestion analysis during the design process to identify and address potential issues early.

- Tip: Use tools like Mentor Graphics Calibre for comprehensive congestion analysis.

Conclusion

Congestion in VLSI is a significant challenge that can impact the performance, power consumption, and manufacturability of integrated circuits. By understanding the causes and implications of congestion, designers can implement effective strategies to mitigate its impact. Optimal floorplanning, efficient placement and routing, layer optimization, buffer insertion, and regular congestion analysis are essential techniques for managing congestion in VLSI designs.

Also Read : fpga architecture in vlsi

To know more about VLSI Course , SuccessBridge VLSI training institute. You can begin your VLSI career by enrolling in the placement-assisted live courses available at SuccessBridge We offer various VLSI online courses. We offer VLSI Physical Design course, Design Verification course, DFT Training , Chip design course many more. Explore VLSI Courses From The Leaders In VLSI Training

For further insights and detailed guidance on VLSI design, stay tuned to our blog. Don’t forget to subscribe for the latest updates and tips from industry experts.