Introduction

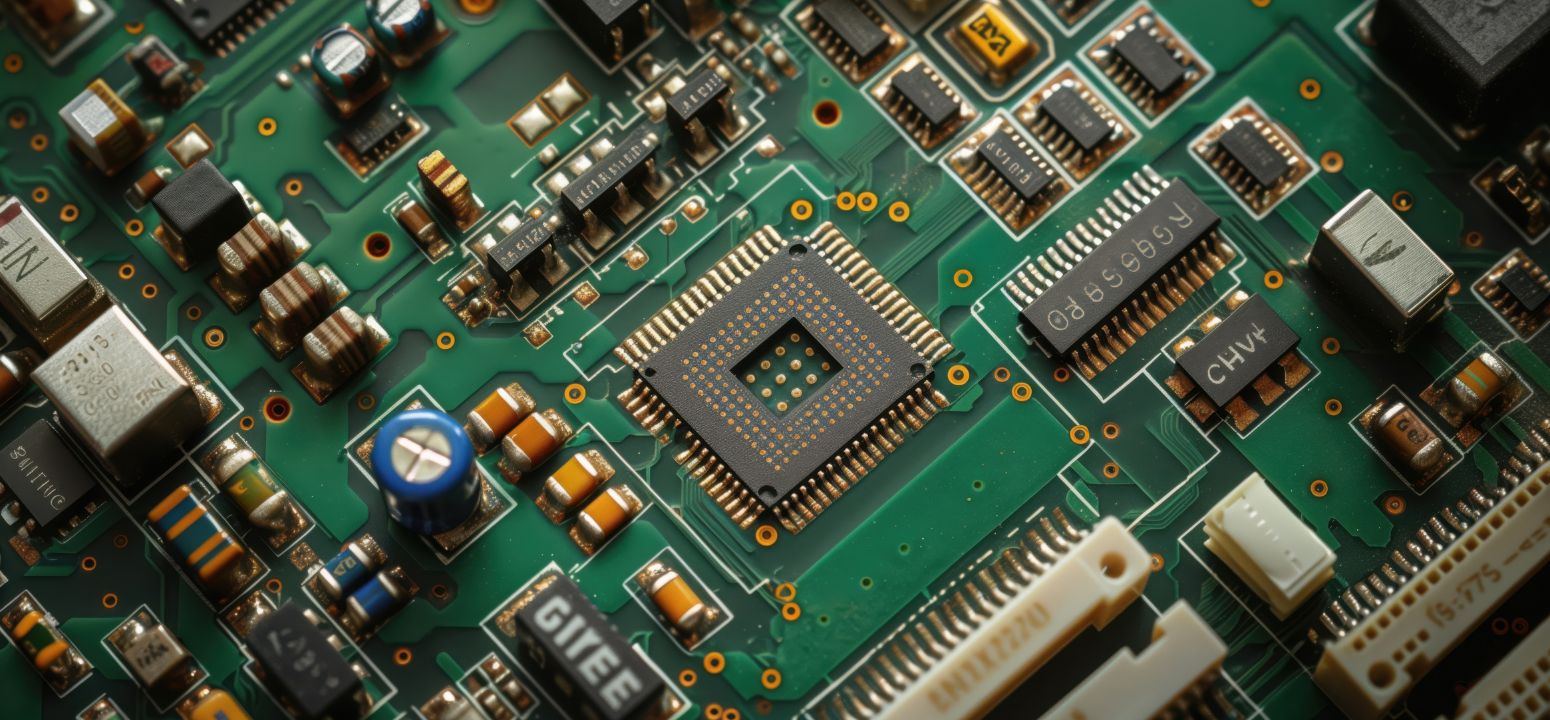

The field of Very Large Scale Integration (VLSI) design is evolving rapidly, requiring engineers to master advanced techniques to stay ahead in the industry. This blog explores the latest methodologies and best practices in advanced VLSI design, helping professionals optimize their workflows and improve chip performance.

Key Topics in Advanced VLSI Design

1. Low-Power Design Techniques

Power consumption is a critical concern in modern VLSI circuits, especially for mobile and IoT devices. Techniques like dynamic voltage scaling, clock gating, and multi-threshold CMOS (MTCMOS) help in reducing power usage while maintaining performance.

2. High-Speed Design Optimization

Achieving high-speed performance in VLSI requires techniques such as pipeline optimization, parallelism, and advanced clock distribution strategies. Clock tree synthesis (CTS) plays a crucial role in reducing clock skew and improving timing performance.

3. Design for Manufacturability (DFM)

To ensure higher yield rates, engineers must consider factors like lithography limitations, process variations, and layout constraints during the design phase. Techniques like Optical Proximity Correction (OPC) and Chemical-Mechanical Planarization (CMP) are widely used to improve manufacturability.

4. Advanced Verification Techniques

With increasing design complexity, verification plays a crucial role in ensuring correctness. Modern techniques like formal verification, assertion-based verification, and hardware emulation accelerate the validation process and improve reliability.

5. 3D ICs and Multi-Die Integration

The semiconductor industry is shifting towards 3D integration and chiplet-based architectures. These approaches improve performance, reduce latency, and enhance power efficiency compared to traditional monolithic designs.

Best Practices for Advanced VLSI Design

- Leverage Hardware Description Languages (HDL)

- Use Verilog and VHDL efficiently to describe digital logic.

- Employ synthesizable coding styles to enhance design portability.

- Optimize for Performance and Power

- Balance trade-offs between speed, power, and area (PPA).

- Utilize low-power design methodologies to extend battery life in mobile applications.

- Utilize Industry-Standard EDA Tools

- Familiarize yourself with tools like Cadence Virtuoso, Synopsys Design Compiler, and Mentor Graphics.

- Automate synthesis, placement, and routing to streamline the design process.

- Focus on Design for Testability (DFT)

- Implement scan chains and built-in self-test (BIST) mechanisms to improve test coverage.

- Use boundary scan techniques for efficient PCB-level testing.

- Stay Updated with Emerging Trends

- Keep track of advancements in AI-driven VLSI design automation.

- Explore new materials like carbon nanotubes and silicon photonics for future chip designs.

Conclusion

Advanced VLSI design requires a deep understanding of optimization techniques, manufacturability considerations, and verification methodologies. By following best practices and leveraging industry-leading tools, engineers can develop high-performance, power-efficient, and reliable semiconductor solutions.