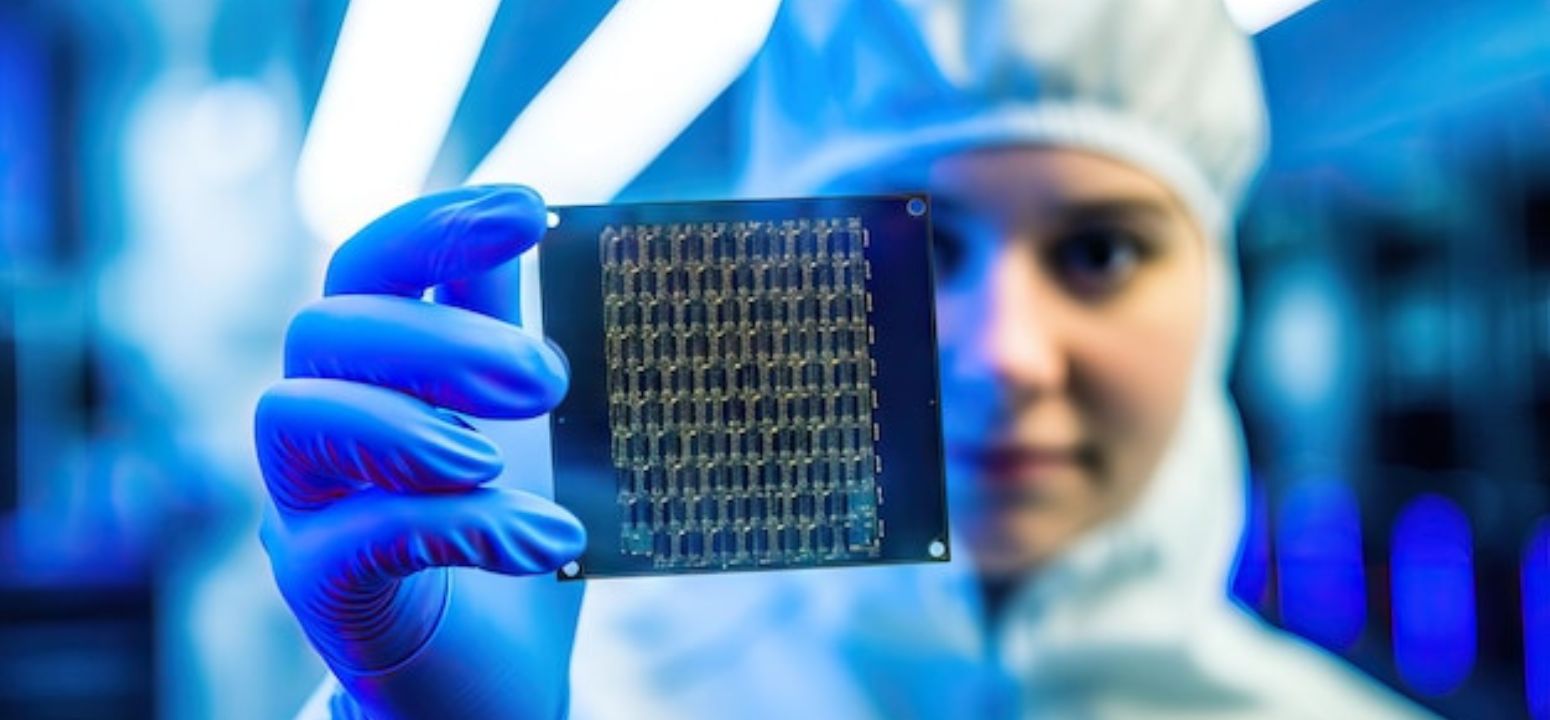

The journey of Very Large Scale Integration (VLSI) has been a cornerstone in the evolution of modern electronics. VLSI,which integrates thousands to millions of transistors on a single chip, has seen advancements by the relentless of Moore’s Law. Scaling in VLSI, the process of shrinking the size of transistors has played a pivotal role in this progress, leading to faster, smaller devices. This blog post delves into the intricacies of scaling in VLSI, its historical context, challenges, and the future outlook.

The Evolution of Scaling in VLSI

The concept of scaling in VLSI dates back to the early days of semiconductor technology. Gordon Moore, co-founder of Intel, famously predicted in 1965 that the number of transistors on a chip would double approximately every two years. This observation, known as Moore’s Law, has been the guiding principle for the semiconductor industry.

Initially, scaling was relatively straightforward: reduce the size of transistors, decrease the power consumption, and increase the clock speed. This approach worked well through the early generations of integrated circuits, leading to the exponential growth of computing power seen in the late 20th and early 21st centuries.

Challenges in Scaling

As technology nodes progressed from micrometers to nanometers, several challenges emerged:

- Physical Limitations: The most significant challenge is the physical limit of silicon-based technology. As transistors approach atomic scales, quantum mechanical effects like tunneling and subthreshold leakage become more pronounced, impacting performance and power efficiency.

- Heat Dissipation: Smaller transistors packed more densely generate more heat. Effective heat dissipation becomes crucial to maintain performance and prevent thermal runaway.

- Manufacturing Complexity: Advanced lithography techniques, such as Extreme Ultraviolet (EUV) lithography, are required to etch ever-smaller features on silicon wafers. These processes are expensive and technologically challenging.

- Variability: At smaller scales, slight variations in manufacturing can lead to significant differences in transistor performance, impacting overall chip reliability and yield.

Innovations Driving Continued Scaling

Despite these challenges, several innovations are driving continued progress in VLSI scaling:

- FinFETs and GAAFETs: The transition from planar transistors to Fin Field-Effect Transistors (FinFETs) and Gate-All-Around FETs (GAAFETs) has improved control over the channel, reducing leakage and enhancing performance.

- Advanced Lithography: EUV lithography has become a key enabler for sub-10nm nodes, allowing more precise patterning of semiconductor devices.

- Material Innovation: Beyond silicon, materials such as graphene, carbon nanotubes, and compound semiconductors like gallium nitride (GaN) are being explored for their superior electrical properties.

- 3D Integration: Stacking multiple layers of circuits in a 3D configuration, known as 3D ICs, enhances performance and reduces latency by shortening the interconnect distances between different components.

- AI and Machine Learning: AI and machine learning algorithms are increasingly used to optimize design processes, predict potential manufacturing issues, and enhance the efficiency of VLSI scaling.

The Future of Scaling in VLSI

The future of VLSI scaling is likely to be defined by a combination of continued dimensional scaling and alternative approaches. Some potential directions include:

- Beyond Moore’s Law: With the physical limits of traditional scaling approaching, the industry is exploring “More-than-Moore” approaches, which integrate additional functionalities (e.g., sensors, power management) on a single chip.

- Neuromorphic Computing: Mimicking the human brain’s architecture, neuromorphic computing promises to revolutionize areas like artificial intelligence and machine learning, offering new paradigms for VLSI design.

- Quantum Computing: While still in its infancy, quantum computing represents a radical shift, leveraging quantum bits (qubits) for exponential increases in computing power for specific tasks.

- Heterogeneous Integration: Combining different types of chips (e.g., processors, memory, sensors) in a single package can provide enhanced functionality and performance, circumventing some limitations of traditional scaling.

Conclusion

Scaling in VLSI has been a driving force behind the technological advancements of the last few decades, enabling the creation of increasingly powerful, efficient, and compact electronic devices. While significant challenges lie ahead, ongoing innovations and new approaches promise to keep pushing the boundaries of what is possible. The journey of scaling in VLSI is far from over, and its future holds exciting potential for further transforming our world.

Also Read : fpga architecture in vlsi

To know more about VLSI Course , SuccessBridge VLSI training institute. You can begin your VLSI career by enrolling in the placement-assisted live courses available at SuccessBridge We offer various VLSI online courses. We offer VLSI Physical Design course, Design Verification course, DFT Training , Chip design course many more. Explore VLSI Courses From The Leaders In VLSI Training

As we continue to explore the frontiers of semiconductor technology, the collaborative efforts of researchers, engineers, and technologists worldwide will be crucial in overcoming obstacles and unlocking new levels of performance and functionality. The next era of VLSI scaling is poised to bring about even more profound changes, paving the way for a future where the limits of technology are continually redefined.